-

Notifications

You must be signed in to change notification settings - Fork 28

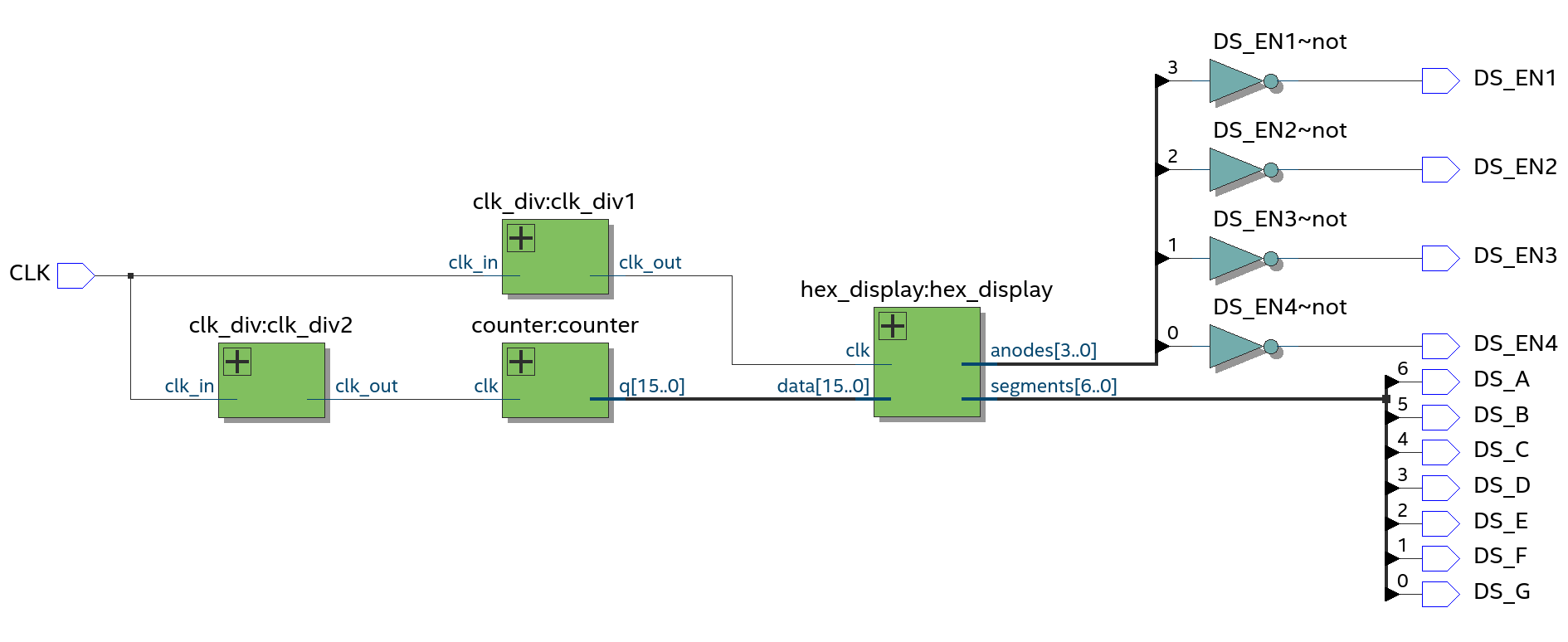

Problem 05: Hex counter

Перейдите в каталог problems/05_hex_counter в вашей локальной копии репозитория. Для синхронизации локального репозтория используется команда git pull.

В результате выполнения прошлых заданий были сделаны парметризуемый делитель частоты на основе двоичного счётчика и блок управления семисегментным индикатором. Дальше предполагается, что они имеют следующие входные и выходные порты:

module hex_display(

input clk,

input [15:0]data,

output [3:0]anodes,

output [6:0]segments

);module clk_div #(parameter X = 1)(

input clk,

output clk_out

);Кроме того, в отдельном файле подготовьте модуль 16-разрядного счетчика со следующими портами:

module counter #(parameter W = 16)(

input clk,

output [W - 1:0]q

);Теперь в текущем каталоге у вас должны быть файлы с кодом модулей делителя частоты, управления семисегментным индикатором и счётчика.

Используя 2 делителя частоты, счётчик и блок вывода на семисегментный индикатор, в модуле top создайте схему вывода данных со счётчика на индикатор.

Проверьте работоспособность схемы с помощью Icarus Verilog. Для удобства просмотра в GTKWave лучше использовать малые значения делителей.

Подберите значения делителей из следующих соображений:

- Частота тактового сигнала

CLK-- 48-50 МГц - Динамическая индикация должна правильно работать

- Счёт должен быть заметен

Запрограммируйте FPGA, визуально оцените правильность работы.