OpTiMSoC is an award-winning an open-source framework primarily written in Verilog which allows you to build your own manycore System-on-Chip by connecting tiles like processors and memories through a Network-on-Chip. The resulting system can then be simulated on a PC or synthesized for an FPGA. You want to know how a SoC really works by taking a deep look inside? You want to evaluate the benefit of a new hardware accelerator? You want to test algorithms to assign tasks efficiently to different processing cores? OpTiMSoC gets you started!

OpTiMSoC comes with an ever growing documentation as well as a lot of sample code that you can use to get started quickly. Depending on the hardware and software you have available, you can start by running a small existing system on an FPGA or simulating it (with Verilator or ModelSim).

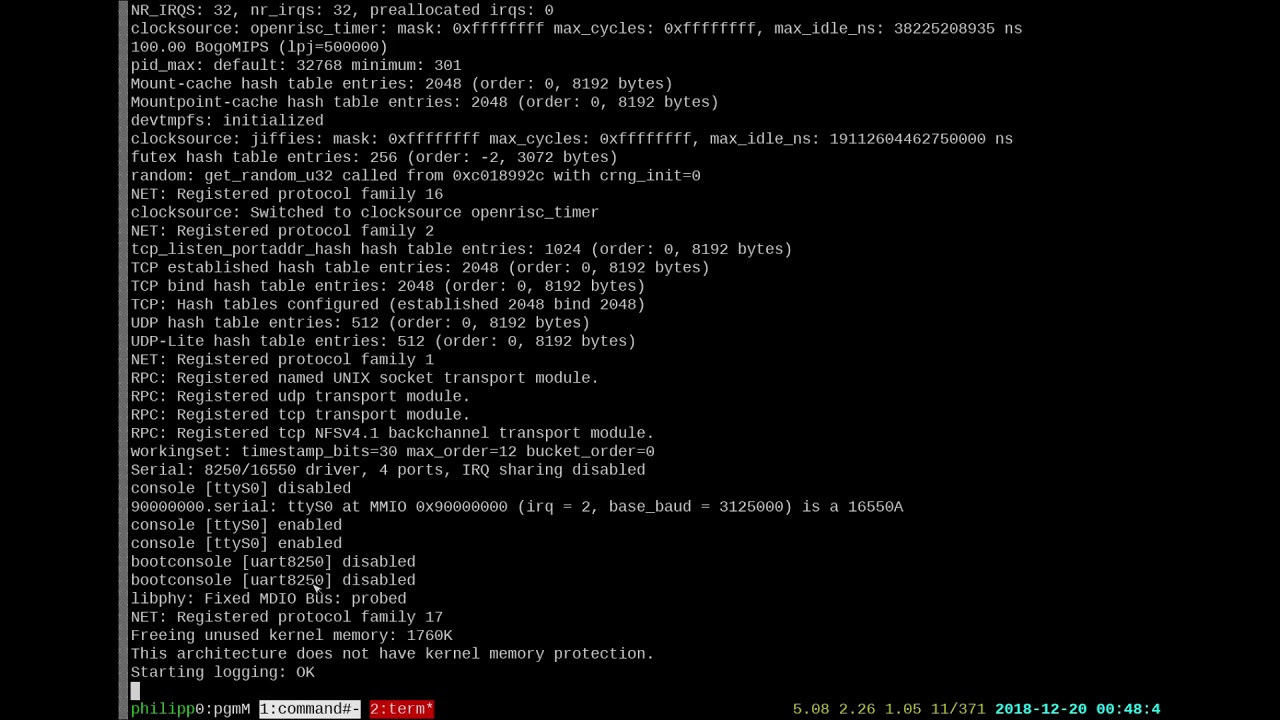

OpTiMSoC can boot Linux! Have a look, and read more about it in our blog.

OpTiMSoC welcomes your contribution! Our web site has more information how to get in touch and contribute. Or simply file an issue or a pull request here on GitHub.

OpTiMSoC is licensed under the permissive MIT license, see COPYING for details.